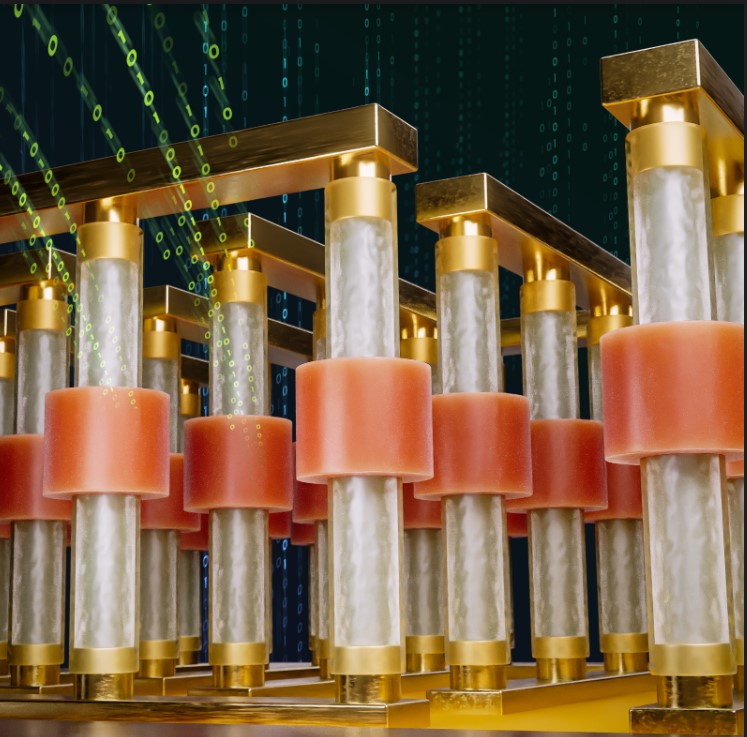

Des transistors verticaux nanométriques pour une électronique 3D

Une équipe du Laboratoire d'analyse et d'architecture des systèmes a mis au point un procédé de fabrication de transistors verticaux miniaturisés, à base de nanofils de silicium, dont les contacts métalliques sont performants et fiables. Pour démontrer la capacité de leur technologie, les chercheurs ont réalisé des "portes logiques", briques de base des circuits intégrés. Ces résultats sont publiés dans la revue ACS Nano Letters.

Des transistors réalisés verticalement dans le matériau semiconducteur, et non plus en technologie planaire, sont une solution pour accroître la compacité des circuits électroniques. Mais jusqu'à présent, leur intégration est limitée par la mauvaise qualité des contacts électriques de ces transistors. C'est pour lever cet obstacle qu'une équipe du Laboratoire d'analyse et d'architecture des systèmes (LAAS-CNRS) a mis au point un procédé qui permet de fabriquer des transistors verticaux avec des contacts métalliques dont la fiabilité et les performances étaient jusqu'ici hors d'atteinte.

Les nouveaux transistors verticaux sont réalisés dans une matrice de nanofils de silicium sur un substrat. Principale innovation du procédé : la réalisation des contacts métalliques n'utilise pas de résine photosensible pour déposer ensuite sélectivement le métal et former des pistes conductrices. En effet, la résine est une source de contamination, à l'origine de la mauvaise qualité des contacts. La technique adoptée par les scientifiques du LAAS consiste à déposer une couche métallique à la base des nanofils, couche qui est ensuite structurée par un procédé de gravure couramment utilisé dans l'industrie des semiconducteurs.

Cette nouvelle méthode à l'avantage d'améliorer sensiblement les performances des contacts métalliques, en diminuant leur résistance électrique. Sa reproductibilité est fiable, d'un transistor à l'autre. Il devient alors possible d'assembler ces transistors pour en faire des dispositifs logiques élémentaires. C'est ce qu'ont démontré les chercheurs en réalisant deux types de cellules logiques (des portes NOR et NAND), qui sont des briques de base pour la plupart des fonctions logiques d'un circuit électronique intégré.

En réalisant ces dispositifs avec des transistors verticaux de taille nanométrique (avec des longueurs de grille inférieures à 20 nm), l'équipe du LAAS a montré le potentiel d'intégration de cette technologie, qui permettraient de réduire d'environ 50% la surface du substrat utilisée, comparée à une technologie planaire. Mais la compacité des dispositifs électroniques peut encore progresser : une prochaine étape sera de réaliser des empilements de plusieurs niveaux de transistors verticaux.

© G. Larrieu, LAAS-CNRS

Références

Logic Gates Based on 3D Vertical Junctionless Gate-All-Around Transistors with Reliable Multilevel Contact Engineering.

Abhishek Kumar, Jonas Müller, Sylvain Pelloquin, Aurélie Lecestre, and Guilhem Larrieu.

ACS Nano Letters 2024, 24, 26, 7825–7832.

https://doi.org/10.1021/acs.nanolett.3c04180

Article disponible sur la base d’archives ouvertes HAL